## 2025 IEEE VLSI Review

서울대학교 전기정보공학부 박사과정 박현준

## **Session 12 Ultra High-speed Wireline**

Session 12는 공정 스케일링(3-5 nm)과 광전 집적, 초저지터 클록, 전방 AFE-후방 DSP의 긴밀한 결합을 통해, 차세대 AI/HPC의 대역폭/와트 한계를 갱신하고 802.3ck·PCle Gen-7 급 표준 호환까지 아우르는 성능을 제시한다.

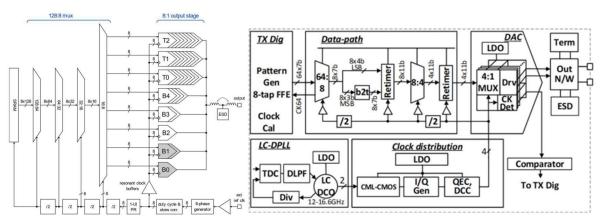

#12-1 본 논문은 5 nm FinFET에서 150 GSa/s, 7-bit SST DAC를 제안한다. 핵심은 (i) SST 유닛 가중치 1·4 병용 분할로 유닛 수를 127→34로 줄여 출력 기생을 대폭 축소하고(T-coil로 ESD C 흡수), (ii) 8-위상 탭드레이라인+듀티/스큐 보정+위상 로테이터로 고정밀 타이밍을 확보하며, (iii) 각 유닛에 CPG가 1-UI/3-UI 펄스를 생성해 3-단 8:1 MUX를 구동하고, 펄스의 앞/뒤 에지를 VT 상승 트랜지스터로 미세 지연해 대역 한계 보상을 선형화한다. 큰 클록 부하(≈1.2 pF/phase)는 공진 클록 버퍼(≈19 GHz, figure-8 L)로 저전력 대스윙을 달성. 이 원리로 초고속·저지터 구동을 구현하여 72.8 GHz tone에서 ENOB 4.1 bit(0.15 GHz에서 6.62 bit), 150 GSa/s@620 mW를 달성했고, 150 Gb/s NRZ / 300 Gb/s PAM-4 아이(soft 10-tap FFE pre-EQ)도 실측으로 확인했다. 결과적으로, 유닛/클록/출력 공설계로 초고속 송신 DAC의 스루풋과 유효 해상도를 동시 달성한 점이 핵심 기여이다.

[12-1] (좌) Prototype DAC architecture block diagram.

[12-2] (우) Block diagram of the 7b DAC-based quarter rate PAM-4 transmitter with per-lane PLL.

#12-2 본 논문은 Intel 18A(GAA RibbonFET + PowerVia BSPDN)에서 7-bit DAC 기반 128

Gb/s PAM-4 TX를 구현해 공정 스케일링 이득을 회로/레이아웃에 직결한다. 핵심은 (i) 백사이드 전력층을 수동소자/배선에 적극 활용(고-Q LC-DCO 인덕터, 20 μm↑ 저저항 백사이드 클록 라우팅, PowerVia로 민감 노드 관통)해 클록 품질·면적·배선 기생을 동시에 낮추고, (ii) LC-DPLL + QEC/DCC + LDO(0.9→0.7 V, >28 dB PSR)로 지터·듀티 오차를 보정하며, (iii) 간소화된 1-UI 펄스제너레이터와 4:1 MUX를 갖춘 7-bit DAC(전/후면 혼용 배선)및 8-tap 디지털 FFE로 고속 선형화를 달성한 점이다. 이 설계로 SNDR 39.6 dB, 0.67 pJ/b(AFE, PLL 포함 0.76 pJ/b), 면적 0.076 mm²를 달성했고, 128 Gb/s PAM-4에서 RLM 0.973, 지터/선형성/CM 노이즈 등 802.3ck 핵심 항목을 충족했다. 결론적으로 백사이드 전력·배선의 시스템적 활용이 저전력·초고집적 TX에 실효적임을 실측으로 입증한다.

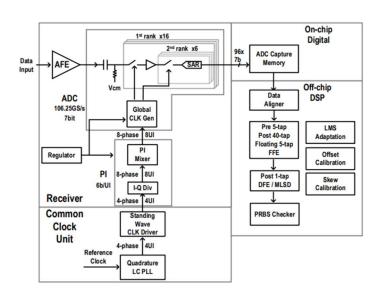

#12-4 본 논문은 4 nm FinFET에서 212.5 Gb/s PAM-4 수신기를 제안하며, 대손실(40 dB @ 53.125 GHz) 채널을 전방 AFE-클록·ADC co-design으로 보상한다. 핵심은 (i) 하이브리드 CTLE + 안정성 강화 CMFB로 푸시-풀 전류 균형을 유지하며 이득/위상 여유를 확보하고, (ii) 상호 인덕티브 결합 Gm-TIA로 입력·출력 인덕터를 결합시켜 Gm-TIA의 고질적대역 확장 한계를 돌파(비결합 대비 ×1.8, 무인덕터 대비 ×2.4 BW)하여 ADC 부하(≈300 fF)까지 직접 구동, (iii) 스탠딩-웨이브 클록 드라이버로 대역통과 특성에 의한 지터 필터링을 수행하고, PI-믹서로 4-위상/1-UI 정밀 위상 정렬을 달성한 점이다. 여기에 96-way TI 7-bit 106.25 GS/s ADC에 ASC 클록·메타안정 보정을 더해 후단 복구 신뢰도를 끌어올렸다. 결과적으로 AFE는 50 GHz에서 13.5 dB 피크(니퀴스트 12.5 dB)를 확보하고, 실측에서 DFE 사용 시 BER 1.86e-4, MLSD 적용 시 5.81e-6(pre-FEC)을 기록해 MLSD의 전력 활용 효율을 입증했다. 칩은 0.56 mm², 675.2 mW(3.2 pJ/b)로, 초고속·고손실 환경에서의 실용 수신 한계를 최신 공정의 AFE+클록+ADC 동시 최적화로 밀어올린 것이 기여이다.

[12-4] A 128Gb/s ADC/DAC Based PAM-4 Transceiver with>45dB Reach in 3nm FinFET

## 저자정보

## 박현준 박사과정 대학원생

● 소속 : 서울대학교

● 연구분야 : 수학

● 이메일 : spp098@snu.ac.kr